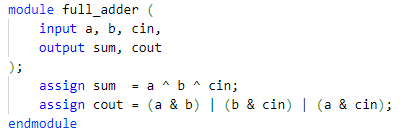

adder를 설계시 (ripple-carry adder)

위와 같이 짜야하는데

이걸 8비트 ripple-carry로 만들려면 8개를 이어붙이고 carry 연결하면 복잡해지고 길어짐

하지만 processor 설계를 예를 들면

1. 설계 목적에 따라 추상화 수준이 다름

전체 데이터 경로(데이터패스)와 제어 흐름이 어떻게 연결되고 동작하는지를 보는 게 목적임

즉, “동작 흐름 설계”가 핵심이지, 개별 게이트까지 구현하는 게 핵심이 아님.

그래서 Adder는 내부 구조보다 “Adder가 있다”는 사실만 명확하게 표현하면 됨.

2. 합성 도구가 알아서 Gate-Level로 바꿔줌

assign sum = a + b;

위 코드는 컴파일러가 내부적으로 carry-lookahead adder, ripple-carry adder 등의 회로로 바꿔줌

👉 결국 게이트로 바뀌긴 하지만, 그걸 직접 짤 필요는 없는 상황

3. 생산성과 유지보수 측면에서 효율적

게이트 레벨로 일일이 짜면:

- 코드 길어지고

- 실수하기 쉽고

- 나중에 바꾸기도 어려워

반면, 추상화된 adder 모듈은:

- 직관적

- 재사용 가능

- 이해하기 쉬움

4. 게이트로 짜야 할 때도 있긴 함

- 초저전력, 초고속 필요할 때

- 레이아웃/면적 최적화가 중요할 때 (ASIC 레벨)

- 수업에서 진짜 add 회로 동작 원리를 익히는 게 목적일 때