Half Adder

1bit a와 b를 받아서 add

sum과 carry 발생

진리표

a b | s c

_______|________

0 0 | 0 0

0 1 | 1 0

1 0 | 1 0

1 1 | 0 1

s = a^b (a xor b)

c = a&b (a and b)

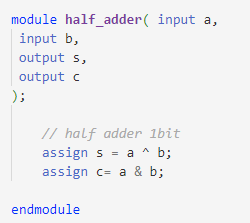

코드

Full Adder

1bit a와 b그리고 cin(carry)를 받아서 add

sum과 carry 발생

진리표

cin a b | s c

___________|________

0 0 0 | 0 0

0 0 1 | 1 0

0 1 0 | 1 0

0 1 1 | 0 1

1 0 0 | 1 0

1 0 1 | 0 1

1 1 0 | 0 1

1 1 1 | 1 1

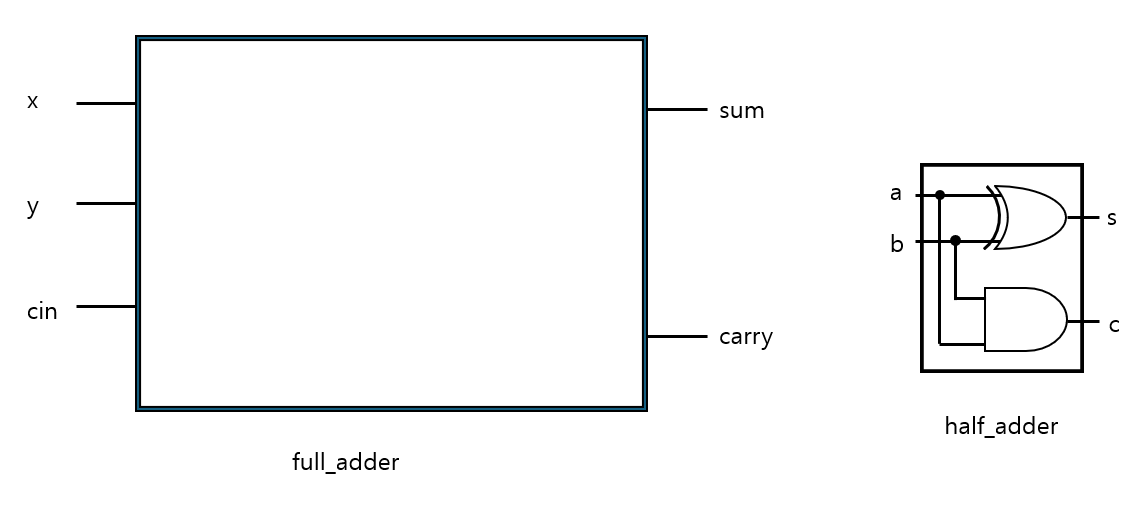

아래 그림처럼 1 bit Half Adder 2개로 1bit Full Adder를 만들 수 있습니다.

위에서 만든 Half Adder를 이용해보겠습니다.

인스턴스화

full_adder 모듈을 만들어 줬습니다.

그림 1을 참고해서 port를 구성해주었습니다.

현재까지의 코드 상황을 그림으로 표현하면 아래와 같습니다

full adder는 겉에 껍데기만 있는 상태고 안에는 아무것도 없는 상태입니다.

그림1에서 보았듯이 여기에 half_adder를 2개 넣어야 합니다.

이때 half_adder를 아래처럼 인스턴스화해서 2개를 만들어 넣어야합니다.

코드는 다음과 같습니다.

노란색으로 강조한 부분처럼 instance화 할 수 있습니다. ('모듈명 인스턴스명' 순서로)

.a, .b, .s, .c는 모듈의 포트명입니다.(half_adder)

우선 포트들을 연결해주겠습니다.

위 그림처럼 연결해주기 위해서 코드를 다음과 같이 해줍니다.

full _adder에 선언해준 port를 안의 인스턴스와 연결해줍니다

다음은 u_half_adder_1과 u_half_adder_2를 아래처럼 연결해주어야 합니다.

하지만 full_adder에서 선언해준 input 과 output들로 u_half_adder_1과 u_half_adder_2를 연결해 줄 수 없습니다.

따라서 새로운 wire를 선언해주고 연결해주어야 합니다

위와 같이 선언해주면 아래 그림과 같은 상태가 됩니다.

여기서 cin도 마저 연결해줍니다.

마지막으로 그림1에서 보았던 것 처럼 u_half_adder_1과 u_half_adder_2에서 나온 각 c를 or를 이용해서 full_adder carry와 연결해주어야 합니다. 그럼 각각의 u_half_adder에서 와이어 1개씩 2개가 필요합니다.

위와 같은 그림을 만들어 주기위해 와이어 w_c1과 w_c2를 선언해줍니다.

그리고 or를 이용해서 carry와 연결 시켜줍니다.

코드는 아래와 같습니다

그럼 최종 코드와 모습은 아래와 같습니다.

이렇게 1bit half_ adder 모듈을 인스턴스화 해서 1bit full adder를 verilog code로 만들 수 있습니다.

'베릴로그' 카테고리의 다른 글

| Verilog 1주차 - Testbench (0) | 2025.03.03 |

|---|---|

| Verilog 1주차 - 기본 작성법 (0) | 2025.03.03 |