RISC 란?

Reduced Instruction Set Computer의 준말로, ISA(CPU의 명령어 집합) 설계방식 중 하나입니다.

명령어 개수가 적고 단순하다는 것이 특징입니다.

반대로 CISC(Comple Instruction Set Computer)가 있습니다.

RISC - V 란?

RISC 기반 명령어 집합의 종류 중 하나 입니다.

RV32I 란?

RISC - V의 가장 기본이 되는 명령어 입니다.

RV32I Base Instruction Set

32bit Instruction Code에 들어있는 정보를 보여줍니다.

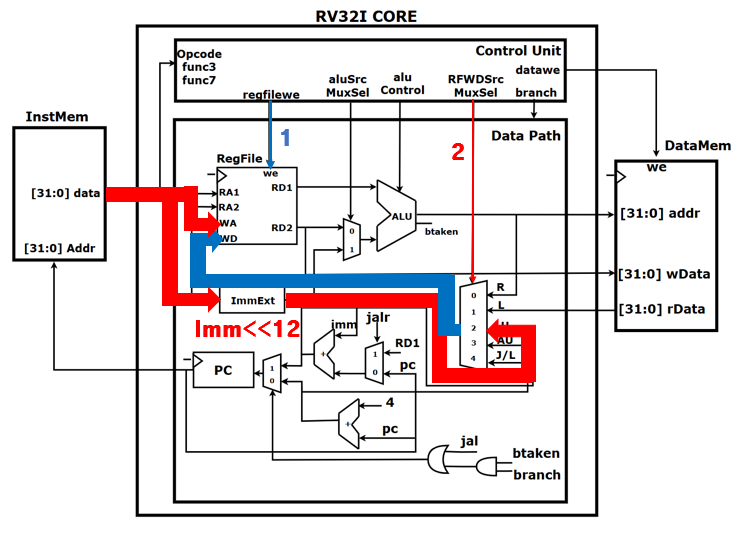

RISC - V, RV32I CORE Block Diagram

동작 순서

1. PC에서 InstMem(ROM)에 명렁 주소를 전송

2. InstMem에서 Control Unit과 DataPath에 32bit Instruction Code를 전송

3. Control Unit은 명령어를 해석하여 Data Path Control Signal을 출력

4. DataPath는 그 Control Signal에 맞게 모듈들이 활성화 및 원하는 연산들이 진행

5. 이후 PC register의 input에는 다음 실행할 명령어의 주소가 들어있음

1~5 반복 ( 매 CLK마다 1~5를 반복합니다)

1. R - type

레지스터간 연산 필요시 사용

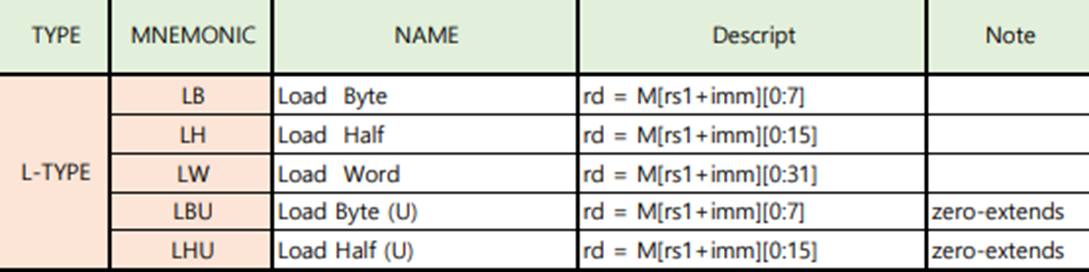

2. L - type

RAM에서 값을 불러올 때 사용

3. I - type

레지스터와 상수 연산시 사용

4. S - type

RAM에 값 저장시 사용

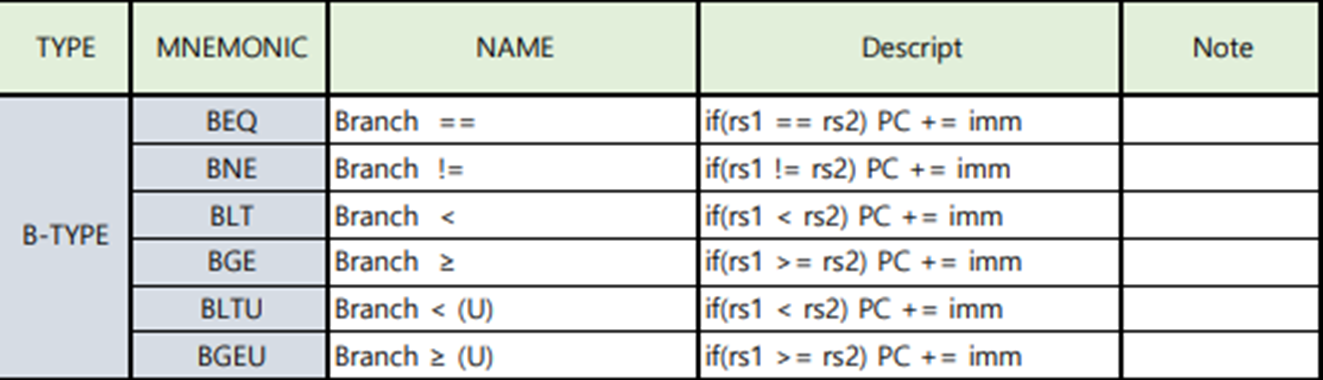

5. B - type

조건에 따른 분기를 위한 명령어

6. LU - type

상위 비트를 다루기 위함

7. AU - type

상위 비트를 다루기 위함

8. J - type

돌아올 주소를 기억하고 함수 호출

9. JL - type

돌아올 주소를 기억하고 함수 호출

출처: https://changsroad.tistory.com/348 [Let's be Developers:티스토리]

'컴퓨터구조' 카테고리의 다른 글

| System Verilog, UVM - 1 (0) | 2025.05.29 |

|---|---|

| I2C 통신 (0) | 2025.05.21 |

| MicroBlaze 사용 및 Vitis 실행하기 (0) | 2025.05.21 |

| SPI Slave Interfac 설계, MicroBlaze (0) | 2025.05.20 |

| SPI 통신 특징 및 다른 통신(UART, I2C와의 비교 (0) | 2025.05.19 |