지난번에 만든 1bit full adder를 이용해 4bit full adder를 만들어보겠습니다.

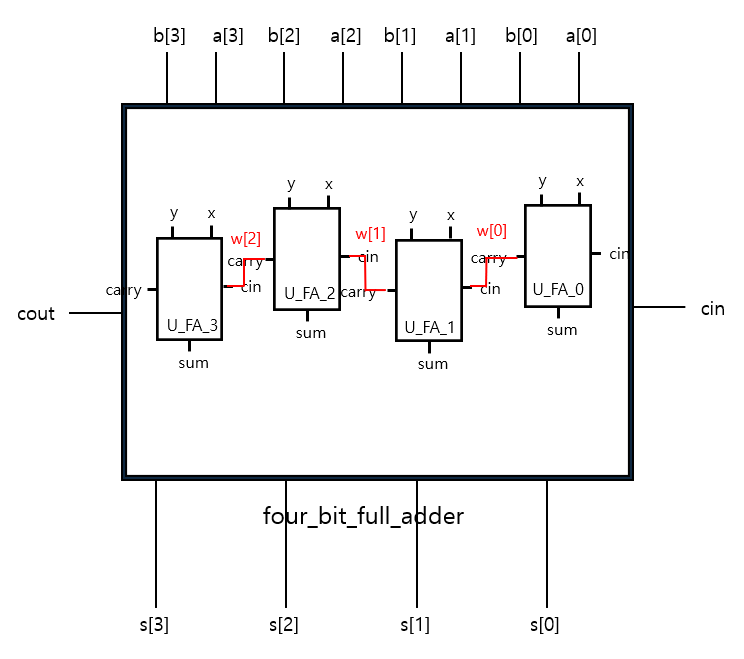

구조는 아래와 같습니다.

지난번에 만든 1bit full adder와 비교하면

x,y 는 An,Bn에 대응되고 sum은 Sn, carry는 Cout, cin은 Cin에 대응 됩니다.

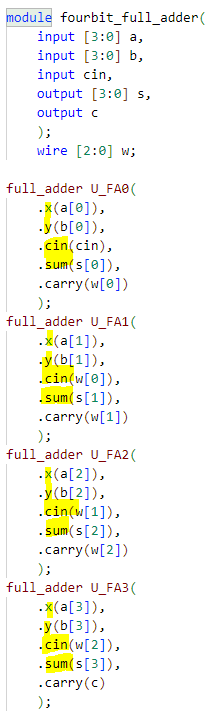

이 full_adder를 인스턴스화 하여 4개를 가져오면 됩니다.

지난번 코드에 input, output을 작성해서 코드를 추가했습니다. (노란색 부분)

아래와 같은 모듈을 만든 겁니다

full adder를 인스턴스화 해서 4개를 만들어줍니다.

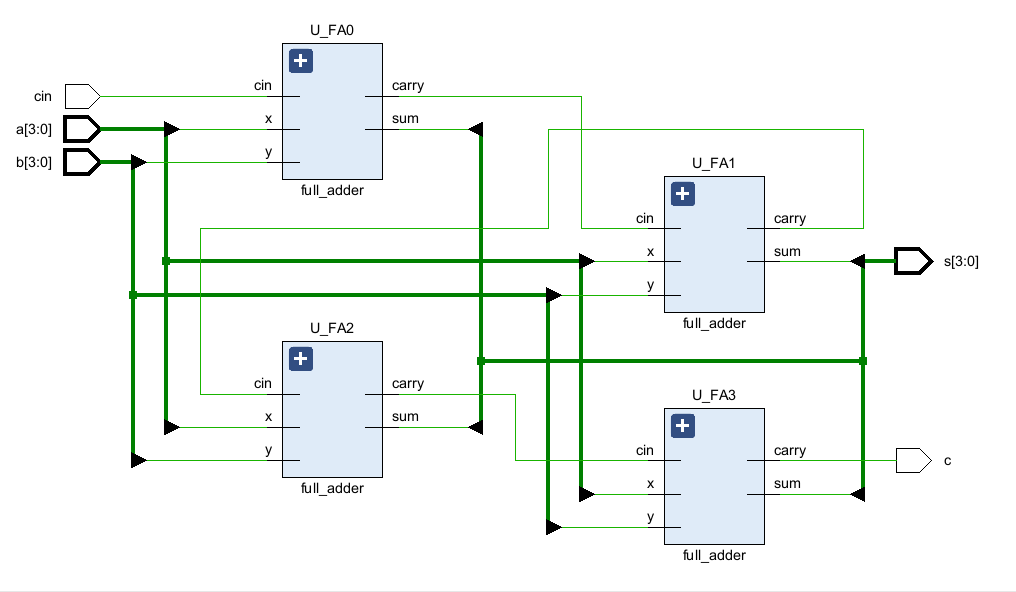

위 그림은 인스턴스화 했을때 모듈의 모습입니다.

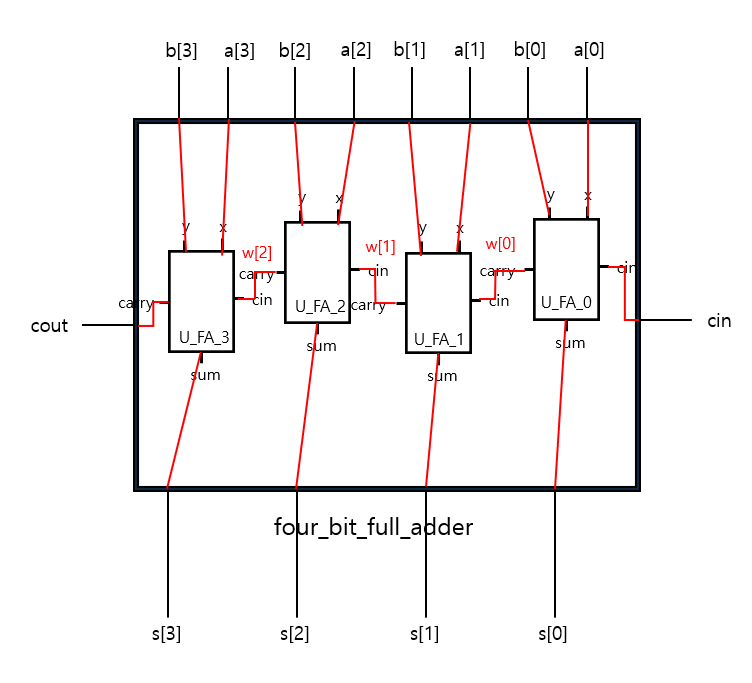

인제 wire를 선언해서 인스턴스화 한 모듈들을 연결해줍니다.(탑모듈 내부안의 '인스턴스화된 모듈'끼리 연결할 때는 wire필요)

탑 모듈인 four_bit_full_adder와 나머지들을 연결해줍니다. (탑모듈과 연결할 때는 wire선언 필요x)

아래는 최종 schematic입니다

'Verilog' 카테고리의 다른 글

| Verilog - CLK divider (0) | 2025.03.20 |

|---|---|

| Verilog - 4bit full adder testbench (2) | 2025.03.16 |

| Verilog - 1bit Half Adder, Full Adder (인스턴스화) (1) | 2025.03.09 |

| Verilog 1주차 - Testbench (0) | 2025.03.03 |

| Verilog 1주차 - 기본 작성법 (0) | 2025.03.03 |