이번에는 3 basys board에서 제공하는 100MHz clk을 이용해 더 낮은 clk인 10Hz clk을 만들어 보겠습니다.

input으로는 clk과 reset을, output으로는 더 낮은 CLK인 o_clk을 선언 해줍니다.

100MHz CLK으로 10Hz CLK을 만들기 위해선 100MHz CLK이 10M개 의 파형을 띄울 때마다 o_clk을 1로 띄웠다가 0으로 만들어 주면 됩니다.

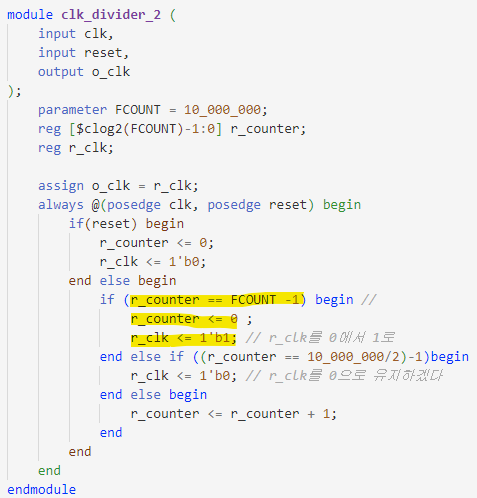

아래는 전체 코드입니다.

10M개의 파형의 개수를 세어야 하므로 parameter로 FCOUNT를 선언해주고 10_000_000으로 초기화 해줍니다.

FCOUNT(10_000_000)만큼의 파형 개수를 세어야 하므로 노란색으로 강조한 부분처럼 r_counter를 선언해줍니다.

always구문 안에서는 output이 reg type이어야 하므로 위처럼 reg r_clk를 선언해주고 output인 o_clk에 r_clk를 assign해줍니다.

100MHz의 CLK에 맞추어 10Hz CLK을 만들 것이기 때문에 CLK의 rising edge에 동작을 할 수 있도록 해줍니다. 그리도 reset이 인가되면 CLK과 r_counter를 0으로 초기화 시켜 줍니다.

만약 reset이 눌리지 않았다면

다음과 같은 step을 가집니다.

1. r_counter가 9_999_999인지?

2. r_counter가 4_999_999인지?

3. 그것도 아니라면 r_counter 1증가

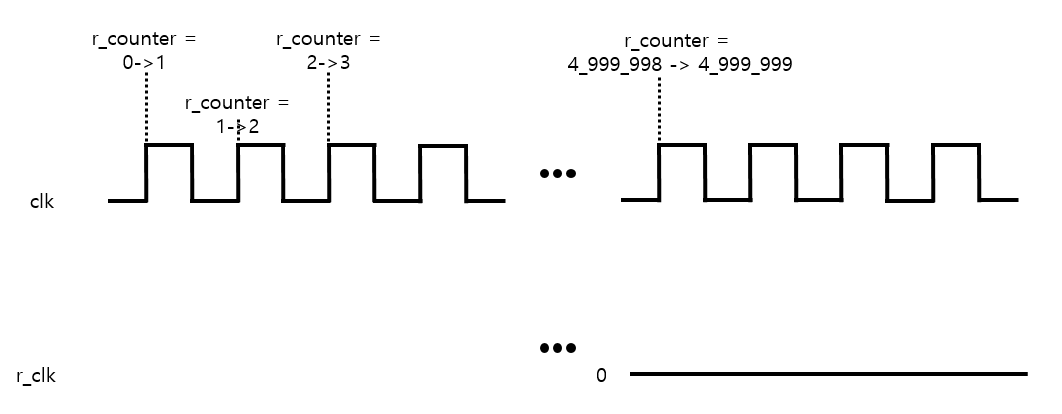

첫 시작은 r_counter가 0이므로 4_999_999가 될 때까지 r_counter는 증가하게 됩니다.

그러다 r_counter가 4_999_999가 되면 r_clk는 0이 됩니다

여태까지 상황을 그림으로 표현하면 아래와 같습니다.

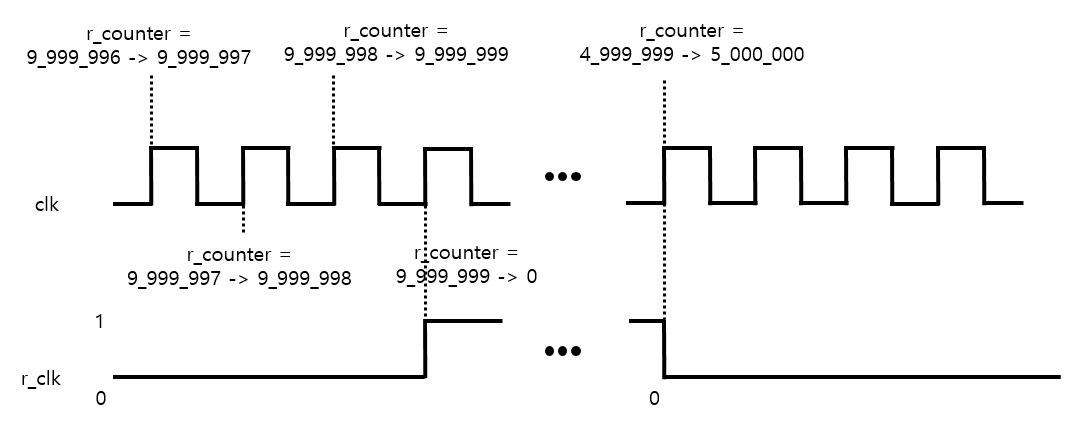

만약 r_counter가 9_999_999까지 증가하게되면 다음 clk에서 r_counter는 0이되고, r_clk가 1로 상승하게 됩니다.

그럼 다시 clk마다 r_counter는 1씩 증가하게 되고 r_counter가 4_999_999 가되면 r_clk은 다시 0으로 떨어지게 됩니다.

이것을 반복하면 10HZ의 r_clk이 생성되게 됩니다.

즉 clk_divider_2의 input으로 clk이 들어오면 출력 port인 o_clk으로 10Hz의 clk이 나오게 됩니다.

'Verilog' 카테고리의 다른 글

| Verilog - 4bit full adder testbench (2) | 2025.03.16 |

|---|---|

| Verilog - 4bit full adder (2) | 2025.03.16 |

| Verilog - 1bit Half Adder, Full Adder (인스턴스화) (1) | 2025.03.09 |

| Verilog 1주차 - Testbench (0) | 2025.03.03 |

| Verilog 1주차 - 기본 작성법 (0) | 2025.03.03 |