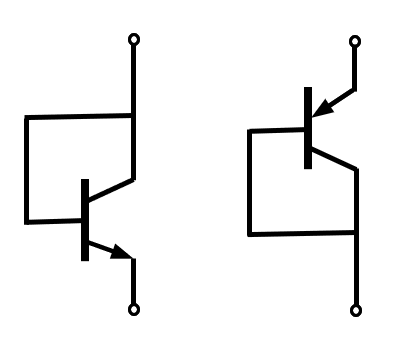

0. Intro 안녕하세요. 오늘은 PMOS의 small signal model에 대해 알아보겠습니다. 그 동안 NMOS위주로 설명했지만 PMOS에 대한 설명도 필요해서 글을 작성하게 됐습니다. PMOS는 NMOS와 모든게 반대라 생각하시면 이해하기 쉽습니다. 1. PMOS그림1은 PMOS의 symbol입니다. Saturation에서 PMOS에 흐르는 전류식은 다음과 같습니다.|ID|=12μpCoxWL(Vsg−|Vth|)2(1+λVsd) ID는 drain에서 source방향으로 흐르는 전류입니다. 절대값을 취했으니 source에서 drain으로 흐르는 전류값을 나타냅니다. 위 식을 입력인 $V_{G..